#### UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA TÉCNICA SUPERIOR DE INGENIEROS DE TELECOMUNICACIÓN

### XXVIII CONVOCATORIA DE PREMIOS

"Ingenieros de Telecomunicación"

Premio "Alcatel-Lucent"

Desarrollo de un adaptador de red para Televisión de Alta Definición sobre IP

Autor: Eduardo Gregorio Quevedo Gutiérrez

Titulación: Ingeniero de telecomunicación

Tutores: Félix B. Tobajas Guerrero

Roberto Sarmiento Rodríguez

# Índice de Contenidos

| 1 RESUMEN DEL PROYECTO FIN DE CARRERA | 1  |

|---------------------------------------|----|

| 1.1 ORIGEN                            | 1  |

| 1.2 Objetivos                         | 2  |

| 1.3 DESARROLLO                        |    |

| 1.4 CONCLUSIONES                      | 5  |

| 2 ORIGINALIDAD                        | 7  |

| 3 RESULTADOS                          | 9  |

| 4 APLICABILIDAD                       | 12 |

# 1.- RESUMEN DEL PROYECTO FIN DE CARRERA

#### **1.1.- ORIGEN**

La *Televisión de Alta Definición* (también conocida como HDTV, del inglés *High Definition TeleVision*) es uno de los formatos que, sumados a la televisión digital (*Digital TeleVision*, DTV), se caracteriza por emitir las señales televisivas en una calidad digital superior a los demás sistemas.

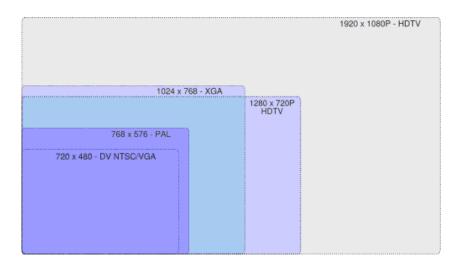

La pantalla HDTV utiliza una proporción de aspecto 16/9. La alta resolución de las imágenes (1920 píxeles × 1080 líneas o 1280 píxeles × 720 líneas) permite mostrar muchos más detalles en comparación con la televisión analógica (de 720 píxeles x 576 líneas según el estándar PAL) o un DVD (*Digital Versatile Disc*) normal. En la Figura 1.1, se puede observar una comparación de la resolución entre los diferentes estándares de televisión.

Figura 1.1.- Comparación de la resolución de los diferentes estándares de televisión

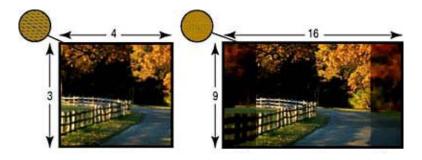

Un sistema HDTV presenta, al menos, el doble de resolución que otro SDTV (*Standard Definition TeleVision*), tal y como se ilustra en la Figura 1.2. Además, los estándares técnicos para transmitir HDTV permiten que se proyecte utilizando una relación de aspecto de 16/9 frente a la relación de aspecto de 4/3 tradicional, sin utilizar franjas negras, lo que permite incrementar la resolución del contenido.

Figura 1.2.- Comparación entre la resolución de dos sistemas: SDTV (izquierda) y HDTV (derecha)

El transporte de vídeo no comprimido HDTV se realiza mediante cable coaxial o fibra, usando para ello el estándar SMPTE-292M. Éste es el medio universal de intercambio entre varios equipos HDTV (por ejemplo cámaras, codificadores, VTRs, sistemas de edición, etc.) y proporciona una conexión digital serie a velocidades de 1'485 Gbps. Este método es ampliamente usado en estudios de producción, ya que evita los típicos artefactos, que aparecen como resultado inevitable de usar ciclos de compresión, así como la latencia subyacente. El término artefacto es utilizado en la ciencia, medicina y procesamiento de datos, para indicar cualquier distorsión percibida y/o cualquier otro error de datos causado por un instrumento de observación o medición, el cual puede provocar una mala interpretación o resultados erróneos. Para el caso de HDTV, un artefacto representa cualquier error sensible causado por un algoritmo de compresión con pérdidas, destacando entre los diferentes tipos de artefacto el efecto de "ruido mosquito", que se muestra en la Figura 1.3.

Figura 1.3.- Zoom de una imagen de una secuencia de alta definición: con artefactos de compresión "mosquito" (izquierda), no comprimida (derecha)

Si se desea realizar el transporte de vídeo no comprimido en una zona amplia, puede utilizarse sin problemas el *bit-stream* 292M sobre conexiones de fibra óptica, si bien la utilización de la tecnología IP (*Internet Protocol*) representa una solución técnicamente viable y más económica.

La televisión sobre IP parece llamada a constituir el siguiente gran paso en el imparable proceso de "todo sobre IP". Si en los últimos años ha sido el concepto, y los primeros despliegues del servicio de VoIP (*Voice over IP*), lo que ha originado el inicio de importantes transformaciones en el mundo de las telecomunicaciones, ahora mismo se están produciendo las transformaciones de este mercado alrededor de los servicios de televisión y vídeo.

El grupo de trabajo AVT (*Audio/Video Transport*) del IETF (*Internet Engineering Task Force*) se ocupa de la estandarización de varios aspectos del transporte de audio y vídeo sobre IP. El AVT ha definido el *Protocolo de Transporte en Tiempo Real* (*Real-time Transport Protocol*) como el estándar adecuado para el transporte en tiempo real sobre IP; es por tanto, este protocolo el adecuado a la hora de transportar vídeo de alta definición sobre IP. RTP es un protocolo de transferencia de datos en tiempo real que desarrolló el IETF en el período comprendido entre 1992 y 1996 a partir del protocolo NVP II (*Network Voice Protocol, versión II*) que en sus principios, que datan de 1979, se usaba tan solo para voz (primera versión del protocolo). RTP se caracteriza por ser un protocolo de transferencia de datos eficaz y por poseer además funciones de control en cuanto a gestión de membresía, sincronización audio-vídeo e informes de calidad periódicos.

Los estándares para el transporte en tiempo real en redes de vídeo sobre IP han alcanzado una relativa madurez, siendo el protocolo dominante RTP. RTP se ejecuta sobre redes UDP/IP (*User Datagram Protocol / Internet Protocol*), heredando sus limitaciones: entrega, como es el caso de la entrega "best effort", o la falta de fiabilidad. Las aplicaciones RTP han desarrollado estrategias sofisticadas para tratar con el *jitter* y la pérdida de paquetes. Se espera, por tanto, que un sistema para la entrega de paquetes HDTV sobre IP use estas características para proporcionar un servicio robusto. Los receptores usan información de las cabeceras para la corrección de la pérdida de paquetes, y para reconstruir la organización de los paquetes a la salida.

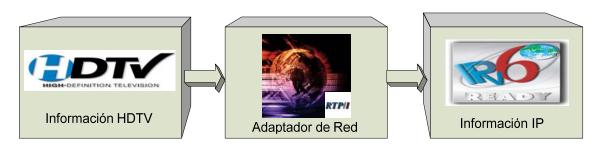

El presente Proyecto Fin de Carrera pretende plantear una arquitectura que posibilite adaptar vídeo no comprimido HDTV al protocolo IP para su transferencia a través de la red, usando para ello el protocolo RTP. Un esquema general que ubica el sistema a realizar (Adaptador de Red) se muestra en la Figura 1.4.

Figura 1.4.- Esquema general de la arquitectura

#### 1.2.- OBJETIVOS

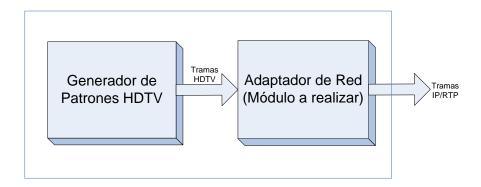

El objetivo principal de este Proyecto Fin de Carrera consiste en el diseño, implementación y verificación funcional de un adaptador de red genérico para HDTV sobre IP compatible con el estándar RTP (*Real -time Transport Protocol*). Se realizará un módulo que tendrá como entrada tramas HDTV y como salida tramas IP de acuerdo al formato RTP. Para la verificación del sistema desarrollado se integrará conjuntamente con un generador de patrones HDTV comercial, siendo el diagrama de bloques final el representado en la Figura 1.5. El generador de patrones HDTV es un componente del fabricante Xilinxs disponible en el mercado, cuya referencia es XAPP682. Este componente será estudiado con detenimiento, de tal forma que la entrada al adaptador de red quede perfectamente caracterizada.

Figura 1.5.- Diagrama de bloques del sistema completo

El diseño de la arquitectura se especificará teniendo en cuenta todas las restricciones impuestas por la entrada y salida de la información, y proponiendo diferentes modelos posibles de diseño antes de llegar a la arquitectura final a desarrollar.

Por otro lado, la implementación final del sistema se realizará en el lenguaje de descripción hardware VERILOG (VERIfying LOGic) a nivel RTL (Register Transfer Level) con el fin de asegurar que el diseño final sea completamente sintetizable, concluyendo con la realización de un prototipo de bajo coste basado en una FPGA (Field Programmable Gate Array) que permita en un futuro caracterizar sus prestaciones reales. Como paso previo al proceso de síntesis de la arquitectura, se realizará un entorno de verificación que permita verificar y refinar el diseño.

#### 1.3.- DESARROLLO

La tecnología está creciendo a pasos agigantados, y lo que hasta hace unos años parecía un gran desafío, como es el caso de la transferencia de HDTV sin comprimir, se está convirtiendo en un pequeño reto mediante el uso de las nuevas redes de fibra óptica. Ello evita los típicos problemas asociados a la compresión, como la aparición de artefactos o la latencia. Sin embargo, las redes de fibra óptica son muy costosas, encontrándose una solución más económica en el transporte del vídeo sobre IP, siendo éste el ámbito en el que se desarrolla este Proyecto Fin de Carrera.

En el desarrollo del presente PFC se han seguido, de forma general, los siguientes pasos:

- Se partió de un análisis pormenorizado de las características principales de la Televisión de Alta Definición (HDTV), prestando especial atención a los parámetros de la señal de HDTV sin compresión, objeto de este PFC. La transferencia de información multimedia a través de IP está ahora mismo en boga, de tal forma que aspectos como la voz sobre IP ya están prácticamente estandarizados; sin embargo la transmisión de alta definición sobre IP ha presentado sus primeros experimentos en los dos últimos años, y la mayoría de ellos suelen ser software.

- Una vez determinada la línea de partida del Proyecto Fin de Carrera, se planteó realizar un Adaptador de Red HDTV sobre IP. El diseño de la arquitectura del Adaptador de Red HDTV sobre IP compatible con el protocolo RTP presentaba, además, los siguientes desafíos iniciales:

- Determinar un mecanismo fiable que permitiera realizar la verificación funcional del sistema; es decir, buscar un dispositivo comercial que generase, de forma fiable tramas HDTV a convertir en tramas IP. Con este fin, se seleccionó el generador de patrones HDTV de la empresa Xilinxs, de referencia XAPP682, que fue exhaustivamente analizado y caracterizado, como se presenta en el Anexo B.

- Estudiar el protocolo IP en cuanto al transporte de datos se refiere, y en particular RTP (Real-time Transport Protocol), que es un protocolo bien definido, ya que tras su primera versión Request For Comments (RFC) 1889 de enero de 1996, ha sido sometido a múltiples revisiones, hasta llegar a una versión que se puede considerar definitiva, a expensas de nuevos estándares que vayan surgiendo, definida en el documento RFC 3550, que data de julio de 2003. Esta versión actualizada se analizó profundamente.

- Estudiar si existe alguna definición propuesta en cuanto a la forma de enviar la información HDTV usando RTP. En este proceso se descubre el trabajo de los ingenieros Gharai y Perkins, que proponen dos líneas de trabajo para el transporte HDTV no comprimido sobre IP:

- · Emulación de circuitos, descrita en el documento RFC 3497.

- · Empaquetamiento nativo, descrito en el documento RFC 4175.

- De entre las dos técnicas propuestas se observa que la segunda de ellas es más flexible, pudiéndose empaquetar cualquier estándar de vídeo HDTV y enviando sólo la información correspondiente al vídeo activo, siendo por ello la técnica seleccionada en el desarrollo de este PFC, la cual se describe en el documento RFC 4175, fechado en septiembre de 2005.

- Una vez todos los frentes teóricos habían sido analizados y meditados, se pasó a plantear el diseño de la arquitectura teniendo en cuenta las restricciones propuestas por la entrada HDTV y la salida mediante empaquetamiento nativo RTP, planteándose inicialmente tres arquitecturas, cuyas características fueron analizadas posteriormente, determinando la que se consideró óptima para el proceso de transporte de los datos HDTV hasta su conversión a tramas RTP. Una vez seleccionada la arquitectura a implementar, se especificaron cada uno de los bloques funcionales de la misma, indicando las restricciones de diseño de cada uno de ellos, los protocolos implicados, así como las interconexiones entre ellos.

- Tras el diseño completo de la arquitectura se realizó su codificación en lenguaje Verilog usando para ello la herramienta de diseño Modelsim. Posteriormente, una vez codificados los bloques funcionales que constituyen la arquitectura desarrollada, se procedió a la verificación funcional. Este proceso de verificación se llevó a cabo a diferentes niveles, verificando la funcionalidad de cada bloque de forma independiente, así como de agrupaciones de módulos relacionados entre sí o *clusters*, y por último, la funcionalidad del sistema completo.

- Finalmente se analizaron los resultados obtenidos, a partir de dos estándares de vídeo considerados, que demuestran la correcta funcionalidad del adaptador para casos extremos. El resto de simulaciones para otros estándares se recogen en el Anexo C.

#### 1.4.- CONCLUSIONES

Mediante el desarrollo especificado en el apartado previo se consiguió especificar un adaptador de red para alta definición sobre IP que verifica las siguientes características:

- Entrada compatible con las características típicas de un formato HDTV:

- Formato de muestreo 4:2:2.

- Señales de luminancia y crominancia de 10 bits.

- Adaptable a cualquier estándar HDTV, debido a que el adaptador se adapta a cualquier flujo de entrada, independientemente del número de líneas por trama y de muestras por línea del mismo.

- La salida del Adaptador de Red proporciona tramas RTP de 32 bits y se adapta a las dos posibilidades en cuanto a la transferencia de datos:

- Ethernet: Máximo tamaño del paquete de 1500 bytes.

- Gigabit Ethernet: Máximo tamaño del paquete de 9000 bytes.

- Ciertas características de los paquetes RTP a la salida, pueden ser caracterizadas desde la entrada del Adaptador de Red.

Se realizó además la síntesis lógica del dispositivo, en el caso particular de este Proyecto Fin de Carrera, la herramienta de síntesis utilizada fue Altera Quartus v5.0. El dispositivo lógico programable seleccionado fue el EP2C20F484C6 de la familia Cyclone II, cuyo tamaño es muy superior al requerido, pero permite simplificar el proceso de síntesis, ya que sólo se quería constatar que el código desarrollado fuera sintetizable.

## 2.- ORIGINALIDAD

Como antecedentes al Proyecto Fin de Carrera realizado, existen algunos trabajos relevantes en el sector de HDTV no comprimido sobre IP:

- Proyecto de la empresa Pacific Western GigaPop (enero de 2005): Representa la primera transferencia multicast de 1'5 GBps de vídeo de alta definición y la primera demostración de videoconferencia multipunto utilizando alta definición no comprimida, realizada entre EEUU y Japón. Desde cada punto remoto, se transmitía vídeo de HD no comprimido (HDNC) y audio sobre IP. El desarrollo de este sistema fue dirigido por la Universidad de Washington.

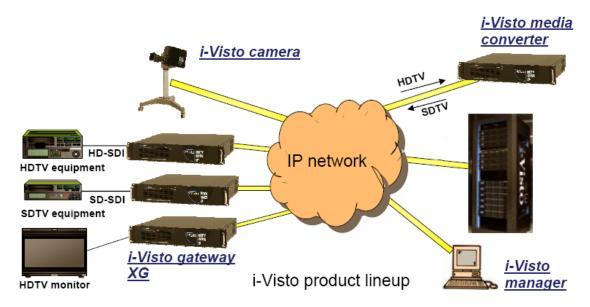

- Proyecto i-Visto de la empresa NTT Communications (enero de 2006): Este sistema, desarrollado en Taipei, es capaz de manejar diez flujos HDTV simultáneamente. Está caracterizado por la transmisión de HDTV no comprimido en tiempo real con fácil adaptación en sistemas basados en IP, tales como WWW (World Wide Web). Posee poco retardo y está basado en un sistema que se maneja desde un PC, como se muestra en la Figura 2.1.

Figura 2.1.- Sistema i-Visto

La originalidad del presente Proyecto Fin de Carrera recae en los siguientes aspectos:

- La especificación del adaptador de red se realiza sobre un dispositivo hardware dedicado, lo cual da lugar a que se minimicen las restricciones implícitas a plantear una solución desde un punto de vista software, debidas principalmente a la elevada velocidad de transmisión que se plantea en HDTV.

- Los formatos de vídeo varían en el número de líneas activas por trama y en el número de muestras activas por línea. El adaptador realizado es capaz de trabajar con cualquier formato de vídeo de alta definición no comprimido, habiendo sido verificado para la gran mayoría de los casos (ver apartado 3).

- El presente Proyecto Fin de Carrera ha abierto una nueva línea de investigación en el Departamento de Ingeniería Electrónica y Automática (DIEA) de la Universidad de Las Palmas de Gran Canaria (ULPGC), dando lugar a las siguientes futuras líneas de investigación:

- \* Fabricación en placa de prototipado del Adaptador de Red desarrollado, conjuntamente con el módulo *Generador de Patrones* HDTV de Xilinx, para su posterior verificación física.

- \* Estudio de la salida del Adaptador de Red, tomando la información RTP en un video-streaming y verificándola mediante un *browser* de vídeo compatible.

- \* Adaptación del código del Adaptador de Red para que sea útil para cualquier formato de muestreo (la versión actual contempla únicamente el formato de muestreo 4:2:2, que es el más usual en HDTV).

- \* Realización de un adaptador red, análogo al desarrollado en este Proyecto Fin de Carrera, pero utilizando la técnica de transporte de HDTV no comprimido sobre IP de emulación de circuitos, para su posterior comparación con la técnica adoptada en el presente Proyecto Fin de Carrera.

# 3.- RESULTADOS

El resultado del Proyecto Fin de Carrera fue un adaptador de red robusto y verificado en prácticamente todos los estándares de HDTV existentes. En cuanto a las principales características del adaptador del Adaptador de Red HDTV sobre IP desarrollado en el presente Proyecto Fin de Carrera, destacan las siguientes:

- La entrada del Adaptador de Red es compatible con las características típicas de un formato HDTV:

- Formato de muestreo 4:2:2.

- Señales de luminancia y crominancia de 10 bits.

- El estándar HDTV puede ser cualquiera, debido a que el adaptador se adapta a cualquier flujo de entrada, independientemente del número de líneas por trama y de muestras por línea del mismo. El proceso de verificación cubrió en detalle los estándares SMPTE 274 1080i y SMPTE 296 720p, si bien, en la Tabla 6.1 se muestran la totalidad de los estándares, cuya compatibilidad se ha comprobado en el presente Proyecto Fin de Carrera.

| Estándar<br>SMPTE | Formato | Tasa de<br>trama (Hz) | Muestras y<br>líneas activas | Muestras y<br>líneas totales |

|-------------------|---------|-----------------------|------------------------------|------------------------------|

| SMPTE 260M        | 1035i   | 30                    | 1920 x 1035                  | 2200 x 1125                  |

| SMPTE 295M        | 1035i   | 25                    | 1920 x 1080                  | 2376 x 1125                  |

| SMPTE 274M        | 1080i   | 30                    | 1920 x 1080                  | 2200 x 1125                  |

| SMPTE 274M        | 1080i   | 25                    | 1920 x 1080                  | 2640 x 1125                  |

| SMPTE 274M        | 1080p   | 30                    | 1920 x 1080                  | 2200 x 1125                  |

| SMPTE 274M        | 1080p   | 25                    | 1920 x 1080                  | 2640 x 1125                  |

| SMPTE 274M        | 1080p   | 24                    | 1920 x 1080                  | 2750 x 1125                  |

| SMPTE 296M        | 1080p   | 60                    | 1280 x 720                   | 1650 x 720                   |

Tabla 3.1.- Estándares HDTV comprobados

- La salida del Adaptador de Red proporciona tramas RTP de 32 bits y teniendo en cuenta dos posibilidades en cuanto a la transferencia de datos:

- Ethernet: El máximo tamaño del paquete es de 1500 bytes, es decir 12000 bits, que conforman como máximo 375 tramas de 32 bits, donde se ha de tener en cuenta el espacio que ocupa la cabecera, que, como máximo es de 30 bits.

- Gigabit Ethernet: El máximo tamaño del paquete es de 9000 bytes, es decir 72000 bits, que conforman como máximo 2250 tramas de 32 bits, donde se ha de tener en cuenta el espacio que ocupa la cabecera, que, como máximo es de 40 bits.

- Ciertas características de los paquetes RTP a la salida, pueden ser caracterizadas desde la entrada del Adaptador de Red, mediante el uso de las siguientes señales:

- *Timestamp:* Marca de referencia temporal de 32 bits, se puede inicializar a un valor determinado, que se actualizará para cada campo (vídeo entrelazado), o para cada trama (vídeo progresivo).

- Sequence\_Number: Número de secuencia de 32 bits, se puede inicializar a un valor determinado, éste valor se incrementará por cada paquete enviado.

- SSRC: Fuente de sincronización de 32 bits, determina la fuente de reloj que está actuando sobre el protocolo RTP.

Se realizó además la síntesis lógica del dispositivo, que es el proceso de convertir una descripción hardware del diseño a alto nivel, en una implementación física optimizada a nivel de primitivas a partir de una biblioteca de células estándar, y bajo unas determinadas restricciones de diseño. Para la realización de la síntesis se emplean en la actualidad herramientas CAD (*Computer Aided Design*) que permiten automatizar el proceso. Por lo general, estas herramientas CAD se basan en un procedimiento iterativo de diseño orientado a obtener el resultado más acorde con las especificaciones de diseño establecidas. Los pasos efectuados por una herramienta de síntesis durante este proceso pueden resumirse en los siguientes:

- Elaboración: En este paso se realiza un análisis del código HDL, generándose unos grafos del sistema que constituyen una representación intermedia utilizada por la herramienta.

- Optimización booleana (independiente de la tecnología).

- Mapeado tecnológico: En este paso se parte de la representación interna optimizada y se implementa su representación a nivel de primitivas usando las células disponibles en la biblioteca tecnológica.

El resultado final del proceso de síntesis es la generación de un netlist que contiene una descripción de las células lógicas que componen el sistema y las interconexiones entre ellas. De esta forma se logra tener conocimiento de la cantidad de lógica empleada (contadores, multiplexores, Flip-Flops, etc.) y hacer un análisis de las prestaciones (frecuencia de reloj, área ocupada, rutas críticas, etc.) que puede llegar a presentar el dispositivo diseñado.

En el caso particular de este Proyecto Fin de Carrera, la herramienta de síntesis utilizada fue Altera Quartus v5.0. Como paso previo al proceso de síntesis, es evidente que resulta necesario seleccionar el dispositivo programable sobre el que se desea mapear el sistema, debiéndose seleccionar aquel que mejor se adapte al diseño, puesto que el tipo, tamaño y número de células lógicas programables disponibles varía de unos dispositivos a otros. Sin embargo, en el caso particular del sistema desarrollado en este Proyecto Fin de Carrera, el dispositivo lógico programable seleccionado fue el EP2C20F484C6 de la familia Cyclone II, cuyo tamaño es muy superior al requerido, pero permite simplificar el proceso de síntesis, ya que sólo se quería constatar que el código desarrollado fuera sintetizable.

A continuación, se destacan los resultados más significativos obtenidos como resultado del proceso de síntesis realizado sobre el Adaptador de Red HDTV sobre IP implementado, en el que no se han tenido en cuenta los bloques de memoria; debido a que su ocupación en la FPGA queda directamente definida con el tamaño de la macro utilizada.

- Familia : Cyclone II.

- Elementos lógicos: 1466/18752 (7%).

Registros: 895.

- Funciones combinacionales: 1255.

- Pins: 170/315 (53%).

- Multiplicadores de 9 bits 2/52 (3%).

- Frecuencia de trabajo: 84.66 MHz, suficiente para HDTV, dónde se necesitan 75 MHz como mínimo.

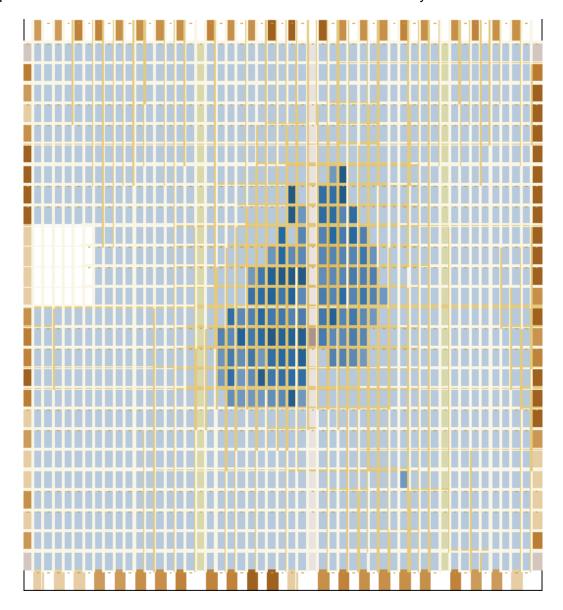

Se representa además, en la Figura 3.1, la ocupación del Adaptador de Red para HDTV sobre IP en la FPGA EP2C20F484C6 de la familia Cyclone II.

Figura 3.1.- Ocupación del Adaptador de Red HDTV sobre IP (en azul oscuro) sobre la FPGA Cyclone II

# 4.- APLICABILIDAD

La aplicabilidad práctica del presente Proyecto Fin de Carrera referida al área de "Nuevos Servicios Interactivos sobre IPTV" queda demostrada en el esfuerzo realizado a la hora de especificar un adaptador de red para HDTV sobre IP que ha completado las siguientes características:

- Permite la entrada de cualquier tipo de vídeo no comprimido independientemente del formato de vídeo (por ejemplo de 1280x720 píxeles o de 1920x1080 píxeles).

- La velocidad de transferencia de datos se puede adaptar a diferentes tamaños de paquete, planteándose en el Proyecto Fin de Carrera los típicos formatos de Ethernet y Gigabit Ethernet.

- La salida de los paquetes IP del adaptador es totalmente caracterizable, siguiendo el formato que a la postre ha demostrado ser el más robusto (empaquetamiento nativo).

- Se ha trabajado una verificación muy completa del dispositivo, como se puede observar en el capítulo 5 del Proyecto Fin de Carrera.

Es por ello que siendo la televisión de alta definición uno de los servicios sobre IP más novedosos y que actualmente están aún en investigación, se plantea este proyecto al premio de Alcatel-Lucent.